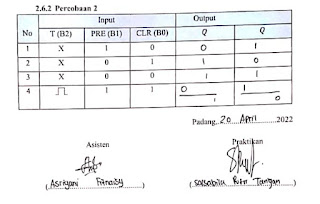

Pada rangkaian T flip-flop adalah bagian dari Jk flip flop. Dimana B1 menuju kaki S dan B0 menuju kaki R dan B2 menuju clk (clock) dimana J dan K menuju VCC. Pada simulasi bersifat aktif low dimana ia akan aktif jika berlogika 0. Pada percobaan pertama B1 berlogika 1 dan B0 berlogika 0 maka output pada Q dan Q’ maka akan Q = 0 dan Q’ = 1. Namun jika B0 dan B1 berlogika 1 dan diberikan clock pada B2 maka akan keluar output Q = 0 dan Q’ = 1 dimana itu adalah kondisi toggle.

1. 1. Apa yang terjadi jika B1 diganti CLK

pada kondisi 2?

Jawaban :

Pada kondisi B2 diganti clock maka output

yang di hasilkan akan berlogika 1. Hal ini karena reset aktif yang membuat Q =

1 dan Q = 0 dan tidak berubah walau dipasangkan clock.

2. 2. Bandingkan hasl percobaan dan teori?

Jawaban :

Pada percobaan dan teori setelah dilakukan

praktikum tidak terdapat perbedaan antara percobaan dan teori.

3. 3. Apa fungsi masing-masing kaki flip-flop yang digunakan

?

Jawaban :

S = set, set menyetel keluaran logika 1 ketika

aktif

R = reset, mereset keluaran logika 0 ketika

aktif

Q = menaampilkan output dari masukan yang

telah diberikan

Q’ = menampilkan output berlawanan kecuali

kondisi terlarang

J dan K = digunakan jika output R dan S

tidak aktif

CLK = clock mengendalikan output JK flip-flop

untuk berubah

Tidak ada komentar:

Posting Komentar