1. Tujuan [kembali]

- Untuk memahami materi tentang transistor JFET

- Untuk mengetahui spesifikasi JFET

2. Alat dan Bahan [kembali]

a. Alat

- voltmeter dc

Berfungsi untuk mengukur besar tegangan pada rangkaian

- Ampermeter

Berfungsi untuk mengukur kuat arus pada rangkaian

- Baterai 12V

Berfungsi sebagai sumber tegangan pada rangkaian

b. Bahan

- Transistor JFET

Spesifikasi

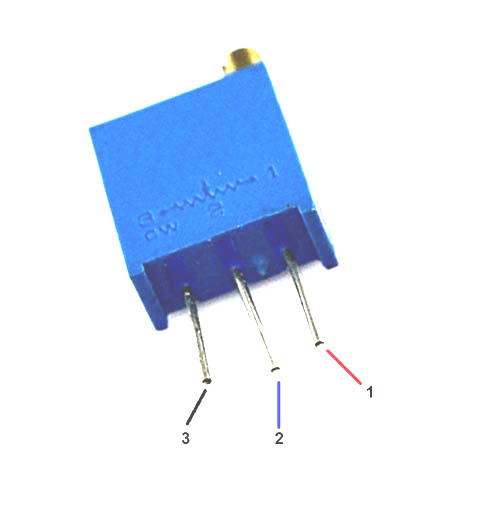

- POT HG

Spesifikasi

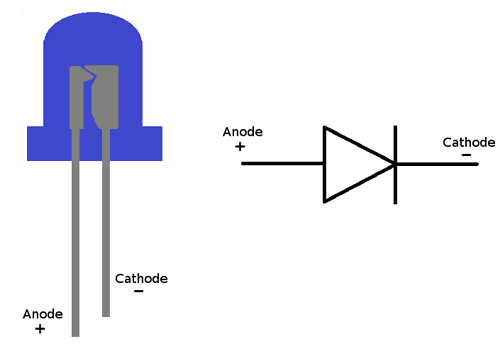

- LED

Spesifikasi

- Resistor

Spesifikasi

3. Dasar Teori [kembali]

5.4 Lembar Spesifikasi JFET

Secara umum, sebuah lembar spesifikasi terdiri dari skala maksimum, karakteristik listrik, konstruksi kasus dan identifikasi terminal, dan yang terakhir yaitu wilayah operasi. Berikut adalah contoh lembar spesifikasi dari JFET 2N5457 n-channel yang disediakan motorola.

Gambar 5.18

1. Skala Maksimum

Daftar skala maksimum biasanya muncul di awal lembar spesifikasi, dengan tegangan maksimum antara terminal tertentu, level arus maksimum, dan tingkat disipasi daya maksimum perangkat. Tingkat maksimum yang ditentukan untuk VDS dan VDG tidak boleh dilampaui di titik mana pun dalam operasi desain perangkat. VDD sumber yang diterapkan dapat melebihi level ini, tetapi level voltase sebenarnya antara terminal ini tidak boleh melebihi level yang ditentukan.

Pembuangan total perangkat pada 25 ° C (suhu ruangan) adalah daya maksimum perangkat dapat menghilang dalam kondisi pengoperasian normal dan ditentukan oleh

Perhatikan kesamaan format dengan persamaan disipasi daya maksimum untuk Transistor BJT. Faktor penurunan nilai dibahas secara rinci di Bab 3, tetapi untuk saat ini kenali bahwa peringkat 2,82 mW / ° C menunjukkan bahwa peringkat disipasi menurun 2,82 mW untuk setiap kenaikan suhu 1 ° C di atas 25 ° C.

2. Karakteristik Listrik

Karakteristik kelistrikan meliputi level VP dalam karakteristik off dan IDSS di karakteristik on. Dalam hal ini VP VGS (off) memiliki range dari 0,5 hingga 6,0 V dan IDSS dari 1 hingga 5 mA. Fakta bahwa keduanya akan berbeda perangkat ke perangkat dengan identifikasi pelat nama yang sama harus dipertimbangkan di proses desain.

3. Konstruksi Kasus dan Identifikasi Terminal

JFET khusus ini memiliki tampilan yang disediakan pada lembar spesifikasi Gambar. 5.18. Identifikasi terminal juga disediakan langsung di bawah gambar. JFET adalah juga tersedia dalam wadah tutup atas, seperti yang ditunjukkan pada Gambar 5.19 dengan identifikasi terminalnya.

Gambar 5.19

4. Wilayah Operasi

Lembar spesifikasi dan kurva yang ditentukan oleh level pinch-off di setiap level VGS menentukan wilayah operasi untuk amplifikasi linier pada karakteristik saluran seperti yang ditunjukkan pada Gambar 5.20. Wilayah ohmik menentukan nilai minimum yang diizinkan VDS di setiap level VGS, dan VDSmax menentukan nilai maksimum untuk parameter ini. IDSS arus saturasi adalah arus drain maksimum, dan maksimum tingkat disipasi daya menentukan kurva yang digambar dengan cara yang sama seperti yang dijelaskan untuk Transistor BJT. Daerah berbayang yang dihasilkan adalah daerah operasi normal untuk amplifier rancangan.

4. Percobaan [kembali]

a. Rangkaian

b. Rangkaian Simulasi [kembali]

c. Video [kembali]

3. kumpulan soal

7. Problem [kembali]

8. Example [kembali]

1. Buat sketsa kurva transfer yang ditentukan oleh IDSS 12 mA dan VP 6 V

Latihan

Buat sketsa kurva transfer untuk perangkat p-channel dengan IDSS 4 mA and VP 3 V.

Tidak ada komentar:

Posting Komentar